Nivelación de desgaste del flash

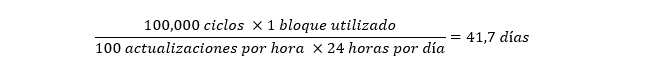

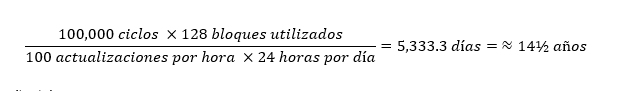

A pesar de la omnipresencia del flash en los sistemas integrados actuales, se siguen produciendo fallos públicos debido al exceso de acceso escritura/borrado que han causado las retiradas de los productos debido a preocupaciones de seguridad. Al inicio del proceso de desarrollo del producto, el equipo debe evaluar la regularidad de los accesos de escritura/borrado y la cantidad de datos que se están escribiendo. Esto se compara con las hojas de datos de las potenciales memorias flash. En el caso de un NAND simple y no gestionado que ofreciera 100 000 ciclos de escritura/borrado por bloque de memoria, escribir 100 actualizaciones por hora cada día a un solo bloque resultaría en una vida útil de:

Al distribuir los datos escritos en muchos bloques de la memoria, la esperanza de vida de la memoria aumenta considerablemente:

Este enfoque de compartir la carga de escritura/borrado entre una gran cantidad de bloques de memoria flash, se conoce como nivelación de desgaste. En sistemas integrados sin un sistema de archivos, el equipo de desarrollo necesitará implementar un enfoque adecuado en el software. El borrado de una página descarga todas las celdas de memoria a 1, mientras que la escritura carga los bits 0. Sin embargo, al usarse una capacidad conocida como programación parcial, una sola página de memoria flash puede ser escrita un número limitado de veces sin borrar hasta borrar las celdas a 0.

Un enfoque de nivelación de desgaste dinámico es capaz de usar esta propiedad para marcar o etiquetar bloques de datos como no válidos después de que la versión más reciente de los datos se haya escrito en una nueva página. Este enfoque requiere que se implemente la dirección de bloques lógicos (LBA): una tabla que mantiene un vínculo entre los archivos escritos y su ubicación física real en la memoria.

Comprender la nivelación del desgaste

Si se utiliza una parte del mismo flash para datos estáticos, como los bootloaders o el código de aplicaciones, estas páginas de memoria no sufren casi ningún desgaste. Los enfoques más avanzados de nivelación de desgaste desplazan los datos estáticos a nuevas ubicaciones, lo cual permite que las páginas de memoria asociadas contribuyan a extender la vida útil general de la memoria flash. Las aplicaciones que usan Linux se benefician de sistemas de archivos que integran la nivelación de desgaste para el almacenamiento flash NAND no gestionado, como JFFS2 y YAFFS.

Otros aspectos que cabe mencionar en cuanto al almacenamiento flash, son el entorno y la velocidad. Las especificaciones de resistencia y retención de datos para el flash se consideran normalmente a 40 °C, pero estas cifras disminuyen rápidamente a temperaturas elevadas. Los dispositivos portátiles y compactos de hoy en día hacen que la gestión del calor sea un desafío, por lo que es fundamental comprender el calentamiento preciso al que puede estar sometido el dispositivo de memoria flash.

El tiempo que se tarda en borrar los bloques de memoria aumenta con el desgaste, por lo que los diseñadores de aplicaciones en tiempo real también deben tener en cuenta los tiempos máximos de borrado de bloques.

A medida que el flash ganó popularidad como alternativa al almacenamiento en placas rotativas, y los teléfonos inteligentes y las tabletas entraron en el mercado, surgió la necesidad de una tecnología flash más rentable. La dependencia de la litografía por sí sola limitaba la densidad máxima alcanzable.

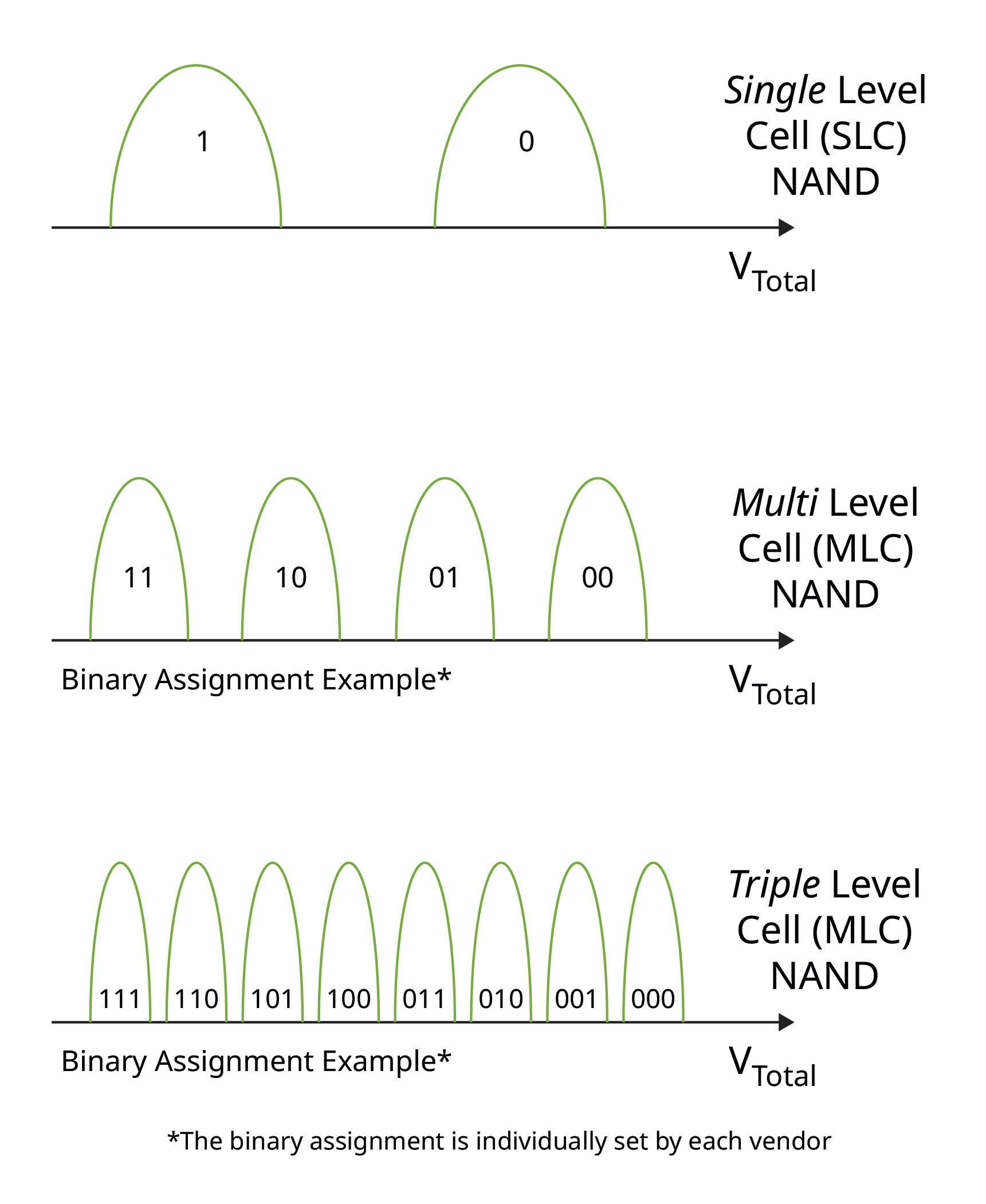

En lugar de almacenar un bit por celda, conocido como celda de un solo nivel (SLC), se introdujo la tecnología de dos bits (celda de varios niveles o MLC) (Figura 1). Aunque esto satisfizo la demanda de los consumidores de almacenamiento asequible de gran capacidad, esta reducción en resistencia de borrado/escritura se volvió una preocupación importante para las aplicaciones industriales y automotrices.

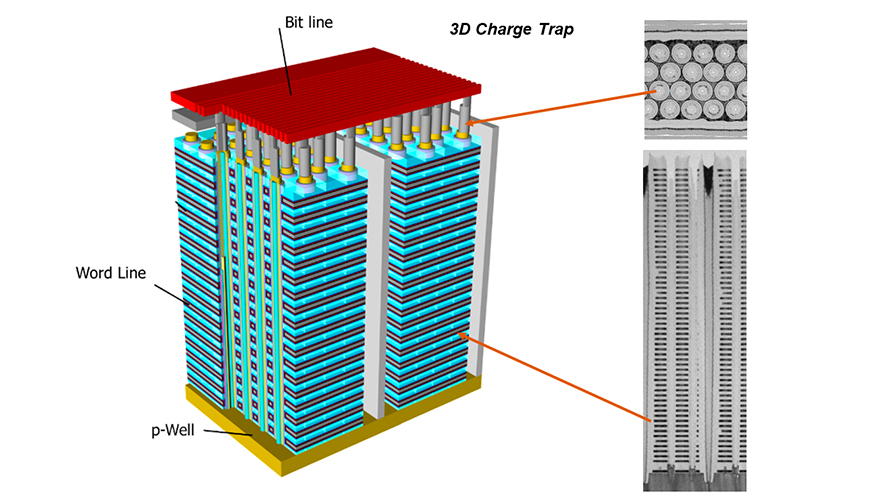

Tecnología Flash 3D

Desde entonces, el desafío de la densidad de almacenamiento se ha abordado utilizando técnicas de fabricación 3D, como la tecnología de memoria flash 3D BiCS Flash (Bit Column Stacked) de Kioxia (Figura 2). Al crear estructuras verticales de celdas de memoria flash, de una forma similar a como veríamos un rascacielos bajo un microscopio, la densidad de almacenamiento queda limitada por la altura alcanzable en combinación con el área de la matriz.

El desplazamiento de las celdas FG planares a las celdas CT verticales de nitruro de silicio proporciona beneficios adicionales. Dado que hay menos presión para reducir el área de cada celda, las celdas CT pueden ser más grandes que las celdas FG. Este mayor tamaño permite almacenar más carga y simplifica la implementación del almacenamiento MLC y de celdas de tres niveles (TLC).

Con una mayor distancia entre las celdas, también se reduce la posibilidad de cruce entre las mismas, lo que hace posibles las celdas de cuatro niveles (QLC, o cuatro bits por celda). Con el BiCS5 de Kioxia que alcanza 112 capas, los productos flash de un solo chip, como el dispositivo THGJFHT3TB4BAIF UFS, ahora están disponibles con una capacidad de almacenamiento de 1 TB.

En general, el flash basado en celdas de CT es más tolerante a los defectos causados por ciclos de escritura/borrado continuos. Sin embargo, el rendimiento de retención de datos es ligeramente inferior al de las celdas flash FG, lo cual se compensa con una comprobación de errores (ECC) más robusta del controlador integrado de un producto flash NAND gestionado o de un controlador externo adecuado.

Debido a que las memorias flash 3D dependen de TLC, con el tiempo los usuarios industriales y automotrices se verán obligados a realizar la migración. Debido a las diferentes características del flash 3D, es probable que muchas aplicaciones también tengan que migrar a soluciones NAND administradas en lugar de desarrollar su propio software de nivelación de desgaste para NAND 3D no gestionado.

Las opciones de flash NAND administradas incluyen e-MMC (Embedded Multimedia Card) y UFS (Universal Flash Storage). El e-MMC es probablemente el más conocido, ya que la tecnología lleva en el mercado 20 años. La mayoría de los dispositivos de sistema en chip (SoC) cuentan con soporte incorporado para la interfaz física, por lo que es fácil de integrar en diseños. Los últimos dispositivos que cumplen con el estándar JEDEC 5.0/5.1 pueden alcanzar velocidades de transferencia de datos de hasta 400 MB/s e incluyen ECC, nivelación de desgaste y gestión de bloqueos defectuosos.

El estándar JEDEC también define una serie de registros que proporciona detalles sobre los ciclos de escritura/borrado consumidos y los bloques de repuesto restantes. Esta es una ventaja considerable con respecto a los NAND no gestionados, que no proporcionan estos registros ni datos sobre la vida útil esperada y, por lo tanto, requieren un controlador externo.

Pseudo SLC con apalancamiento

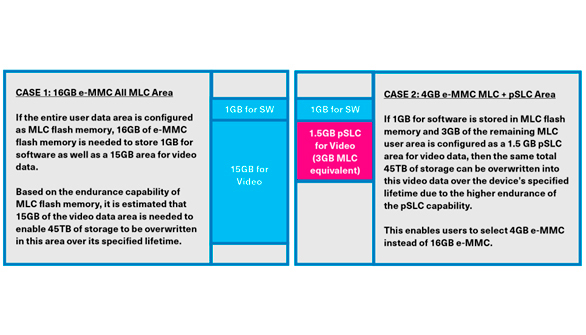

Los dispositivos MLC y TLC NAND flash e-MMC se pueden configurar con una partición pseudo-SLC (pSLC) para aquellos a los que les preocupa la resistencia, la retención de datos y el rendimiento de escritura. Esto reduce los datos almacenados por celda a 1 bit, reduciendo la capacidad MLC a la mitad (dos bits a uno) y la capacidad TLC a un tercio (tres bits a uno). Como resultado, el modo pSLC puede permitir entre 5 y 10 veces más ciclos de escritura/borrado de lo que sería posible de otro modo con MLC o TLC nativos.

El pSLC también puede reducir la capacidad de almacenamiento total necesaria para implementar la misma aplicación. Por ejemplo, el análisis de carga de trabajo puede indicar que se necesitan 15 GB de memoria MLC para almacenar 45 TB de datos de vídeo durante la vida útil especificada de un producto. En combinación con 1 GB para software, esto requeriría un e-MMC de 16 GB. Al usar una partición pSLC, la misma carga de trabajo requiere una partición de 1,5 GB (3 GB de almacenamiento MLC), reduciendo la capacidad total del dispositivo necesaria a solo 4 GB (Figura 3).

En comparación con la última tecnología de unidad de estado sólido (SSD), los usuarios de flash incorporado se quejan de la falta de datos de desgaste y vida útil disponibles dentro del dispositivo. Aunque no es muy probable que esto cambie para el e-MMC, JEDEC está respondiendo a esta necesidad en los estándares de dispositivos UFS. Al ser una tecnología actual y en combinación con sus velocidades de transferencia más altas (2,33 GB/s), soporte para duplex completo y mejor eficiencia energética, UFS es la solución NAND administrada preferida cuando se requieren capacidades superiores a 32 GB, y el SoC elegido incluye la interfaz.

Resumen

Las fuerzas del mercado han forzado a los fabricantes de flash NAND a ofrecer una densidad de dispositivos cada vez mayor utilizando la última tecnología de interfaz de vanguardia. El cambio al flash 3D NAND está bien establecido, lo que significa que los dispositivos tradicionales SLC NAND no gestionados y el desarrollo de la nivelación de desgaste de software dejarán de existir con el tiempo. Debido a la diferencia de tecnología entre el flash planar y el flash 3D, aquellos que necesiten desarrollar software de nivelación de desgaste tendrán que colaborar estrechamente con los fabricantes para desarrollar los algoritmos necesarios. Almacenar múltiples bits por celda es el estándar para el flash NAND actual. Sin embargo, para aquellos que desean mejorar la resistencia y la vida útil del almacenamiento, el pSLC es a menudo una alternativa aceptable. Los flash NAND gestionados, como e-MMC y UFS, simplifican considerablemente la implementación. Sin embargo, el uso de estos dispositivos requiere un análisis minucioso de la carga de trabajo proyectada durante la vida útil para garantizar que el almacenamiento no volátil no se agote prematuramente.